# Intel® Server Board S5000VSA

## **Technical Product Specification**

Intel order number - D36978-004

**Revision 1.0**

April 2006

**Enterprise Platforms and Services Division - Marketing**

## Revision History

| Date       | Revision<br>Number | Modifications             |

|------------|--------------------|---------------------------|

| April 2006 | 1.0                | Initial external release. |

|            |                    |                           |

## **Disclaimers**

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

This document contains information on products in the design phase of development. Do not finalize a design with this information. Revised information will be published when the product is available. Verify with your local sales office that you have the latest datasheet before finalizing a design.

The Intel® Server Board S5000VSA may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel Corporation server baseboards contain a number of high-density VLSI and power delivery components that need adequate airflow to cool. Intel's own chassis are designed and tested to meet the intended thermal requirements of these components when the fully integrated system is used together. It is the responsibility of the system integrator that chooses not to use Intel developed server building blocks to consult vendor datasheets and operating parameters to determine the amount of air flow required for their specific application and environmental conditions. Intel Corporation can not be held responsible if components fail or the server board does not operate correctly when used outside any of their published operating or non-operating limits.

Intel, Pentium, Itanium, and Xeon are trademarks or registered trademarks of Intel Corporation.

\*Other brands and names may be claimed as the property of others.

Copyright © Intel Corporation 2006.

## **Table of Contents**

| 1.                  | Introdu  | uction                                             | 11 |

|---------------------|----------|----------------------------------------------------|----|

| 1.1 Chapter Outline |          | Chapter Outline                                    | 11 |

| 1                   | .2       | Server Board Use Disclaimer                        | 11 |

| 2.                  | Intel® S | Server Board S5000VSA Overview                     | 12 |

| 2                   | 2.1      | Intel® Server Board S5000VSA Feature Set           | 12 |

| 2                   | 2.2      | Server Board Layout                                | 13 |

|                     | 2.2.1    | Server Board Connector and Component Layout        | 13 |

|                     | 2.2.2    | Server Board Mechanical Drawings                   | 15 |

|                     | 2.2.3    | Server Board ATX I/O Layout                        | 18 |

| 3.                  | Functi   | onal Architecture                                  | 19 |

| 3                   | 3.1      | S5000V Controller Hub (MCH)                        | 20 |

|                     | 3.1.1    | Processor Sub-system                               | 20 |

|                     | 3.1.2    | Memory Sub-system                                  | 22 |

| 3                   | 3.2      | Enterprise South Bridge (ESB2-E)                   | 24 |

|                     | 3.2.1    | PCI Sub-system                                     | 25 |

|                     | 3.2.2    | SATA Support                                       | 25 |

|                     | 3.2.3    | Parallel ATA (PATA) Support                        | 26 |

|                     | 3.2.4    | USB 2.0 Support                                    | 27 |

| 3                   | 3.3      | Video Support                                      | 27 |

| 3                   | 3.4      | Network Interface Controller (NIC)                 | 29 |

| 3                   | 5.5      | Super I/O                                          | 30 |

| 4.                  | Platfor  | m Management                                       | 32 |

| 4                   | .1       | Power Button                                       | 32 |

| 4                   | 2        | Sleep States Supported                             | 32 |

|                     | 4.2.1    | S0 State                                           | 32 |

|                     | 4.2.2    | S1 State                                           | 32 |

|                     | 4.2.3    | S4 State                                           | 33 |

|                     | 4.2.4    | S5 State                                           | 33 |

| 4                   | .3       | Wakeup Events                                      | 33 |

|                     | 4.3.1    | Wakeup from S1 Sleep State                         | 33 |

|                     | 4.3.2    | Wakeup from S3 Sleep State (BFAD Workstation Only) | 33 |

|                     | 4.3.3    | Wakeup from S4 and S5 States                       | 33 |

| 4.4      | AC Power Failure Recovery                                      | 33 |

|----------|----------------------------------------------------------------|----|

| 4.5      | PCI PM Support                                                 | 33 |

| 4.5.1    | RESET# Control                                                 | 34 |

| 4.5.2    | PCI Vaux                                                       | 34 |

| 4.6      | System Management                                              | 34 |

| 4.6.1    | CPU Thermal Management                                         | 34 |

| 4.7      | System Fan Operation                                           | 35 |

| 4.8      | Light Guided Diagnostics - System Status and FRU LEDs          | 35 |

| 5. Conn  | ector / Header Locations and Pin-outs                          | 37 |

| 5.1      | Board Connector Information                                    | 37 |

| 5.2      | Power Connectors                                               | 38 |

| 5.3      | Control Panel Connector                                        | 39 |

| 5.4      | I/O Connectors                                                 | 40 |

| 5.4.1    | VGA Connector                                                  | 40 |

| 5.4.2    | NIC Connectors                                                 | 41 |

| 5.4.3    | ATA-100 Connector                                              | 42 |

| 5.4.4    | SATA Connectors                                                | 43 |

| 5.4.5    | Serial Port Connectors                                         | 43 |

| 5.4.6    | Keyboard and Mouse Connector                                   | 44 |

| 5.4.7    | USB Connector                                                  | 45 |

| 5.5      | Fan Headers                                                    | 46 |

| 6. Jump  | er Block Settings                                              | 47 |

| 6.1      | Recovery Jumper Blocks                                         | 47 |

| 6.2      | BIOS Select Jumper                                             | 48 |

| 6.3      | Other Configuration Jumpers                                    | 48 |

| 7. Light | Guided Diagnostics                                             | 49 |

| 7.1      | 5 V STBY                                                       | 49 |

| 7.2      | Fan Fault LEDs                                                 | 49 |

| 7.3      | System ID LED, System Status LED and Post Code Diagnostic LEDs | 49 |

| 7.4      | DIMM Fault LEDs                                                | 49 |

| 7.5      | Processor Fault LEDs                                           | 51 |

| 8. Desig | n and Environmental Specifications                             | 52 |

| 8.1      | Server Board Design Specification                              | 52 |

| 8.2      | Processor Power Support                                        | 53 |

| 8.3      | Power Supply Specifications                                    | 53 |

|    | 8.3.1     | Output Power / Currents                               | 54 |

|----|-----------|-------------------------------------------------------|----|

|    | 8.3.2     | Grounding                                             | 55 |

|    | 8.3.3     | Standby Outputs                                       | 55 |

|    | 8.3.4     | Remote Sense                                          | 55 |

|    | 8.3.5     | Voltage Regulation                                    | 55 |

|    | 8.3.6     | Dynamic Loading                                       | 56 |

|    | 8.3.7     | Capacitive Loading                                    | 56 |

|    | 8.3.8     | Closed loop stability                                 | 56 |

|    | 8.3.9     | Common Mode Noise                                     | 56 |

|    | 8.3.10    | Ripple / Noise                                        | 57 |

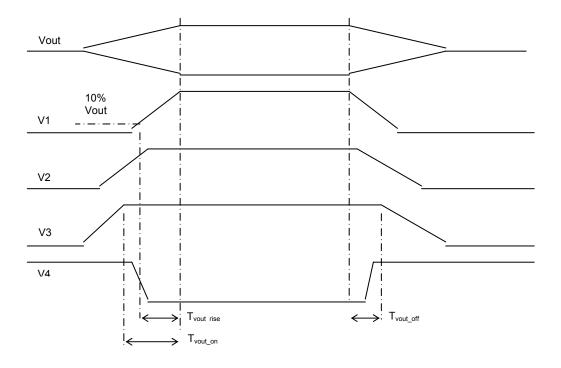

|    | 8.3.11    | Timing Requirements                                   | 57 |

|    | 8.3.12    | Residual Voltage Immunity in Standby mode             | 59 |

| 9. | Regulat   | tory and Certification Information                    | 60 |

| Ć  | 9.1       | Product Regulatory Compliance                         | 60 |

|    | 9.1.1     | Product Safety Compliance                             | 60 |

|    | 9.1.2     | Product EMC Compliance – Class A Compliance           | 61 |

|    | 9.1.3     | Certifications / Registrations / Declarations         | 61 |

| Ś  | 9.2       | Product Regulatory Compliance Markings                | 62 |

| Ć  | 9.3       | Electromagnetic Compatibility Notices                 | 63 |

|    | 9.3.1     | FCC Verification Statement (USA)                      | 63 |

|    | 9.3.2     | ICES-003 (Canada)                                     | 63 |

|    | 9.3.3     | Europe (CE Declaration of Conformity)                 | 64 |

|    | 9.3.4     | VCCI (Japan)                                          | 64 |

|    | 9.3.5     | BSMI (Taiwan)                                         | 64 |

|    | 9.3.6     | RRL (Korea)                                           | 64 |

|    | 9.3.7     | CNCA (CCC-China)                                      | 65 |

| Ć  | 9.4       | Restriction of Hazardous Substances (RoHS) Compliance | 65 |

| Αp | pendix A  | A: Integration and Usage Tips                         | 66 |

| Αp | pendix B  | 3: Sensor Tables                                      | 67 |

| Αp | pendix C  | C: POST Code Diagnostic LEDs                          | 77 |

| GI | ossary    |                                                       | 81 |

| Re | ference I | Documents                                             | 84 |

## **List of Figures**

| Figure 1. Major Board Components                                                       | 14 |

|----------------------------------------------------------------------------------------|----|

| Figure 2. Intel <sup>®</sup> Server Board S5000VSA – Key Connectors and LED Indicators | 15 |

| Figure 3. Intel <sup>®</sup> Server Board S5000VSA – Mounting Hole Locations           | 16 |

| Figure 4. Intel <sup>®</sup> Server Board S5000VSA – Duct keepout Detail               | 17 |

| Figure 5. Intel <sup>®</sup> Server Board S5000VSA ATX I/O Layout                      | 18 |

| Figure 6. Intel <sup>®</sup> Server Board S5000VSA Functional Block Diagram            | 19 |

| Figure 7. CEK Processor Mounting                                                       | 21 |

| Figure 8. Minimum Two DIMM Memory Configuration                                        | 24 |

| Figure 9. Recommended Four DIMM Configuration                                          | 24 |

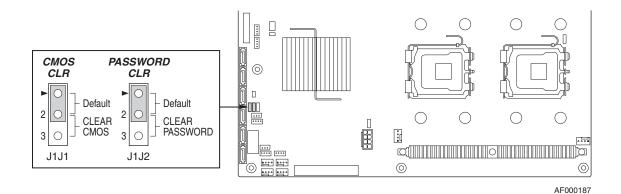

| Figure 10. Recovery Jumper Blocks (J1J1, J1J2)                                         | 47 |

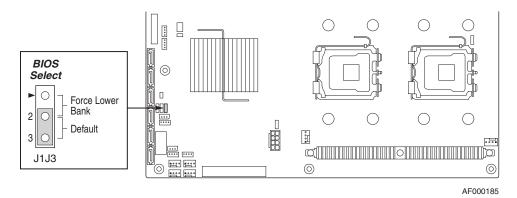

| Figure 11. BIOS Select Jumper (J3H1)                                                   | 48 |

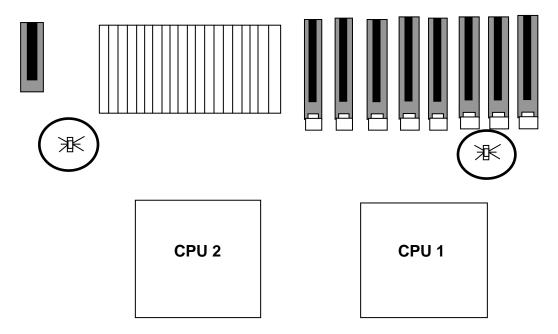

| Figure 12. System ID LED and System Status LED Locations                               | 49 |

| Figure 13. DIMM Fault LED Locations                                                    | 50 |

| Figure 14. Processor Fault LED Locations                                               | 51 |

| Figure 15. Output Voltage Timing                                                       | 58 |

## **List of Tables**

| Table 1. Processor Support Matrix                                                                  | 20 |

|----------------------------------------------------------------------------------------------------|----|

| Table 2. I <sup>2</sup> C Addresses for Memory Module SMB                                          | 22 |

| Table 3. Maximum 8 DIMM System Memory Configruation – x8 Single Rank                               | 23 |

| Table 4. Maximum 8 DIMM System Memory Configuration – x4 Dual Rank                                 | 23 |

| Table 5. Video Modes                                                                               | 28 |

| Table 6. Video Memory Interface                                                                    | 28 |

| Table 7. NIC Status LED                                                                            | 29 |

| Table 8. Serial A Header Pin-out                                                                   | 31 |

| Table 9 Summary of LEDs on the Intel® Server Board S5000VSA                                        | 36 |

| Table 10. Board Connector Matrix                                                                   | 37 |

| Table 11. Power Connector Pin-out (J9C1)                                                           | 38 |

| Table 12. 12V Power Connector Pin-out (J4K1)                                                       | 38 |

| Table 13. Power Supply Signal Connector Pin-out (J1K1)                                             | 39 |

| Table 14. Front Panel SSI Standard 24-pin Connector Pin-out (J1F1)                                 | 39 |

| Table 15. VGA Connector Pin-Out (J7A1)                                                             | 40 |

| Table 16. RJ-45 10/100/1000 NIC Connector Pin-Out (JA6A1, JA6A2)                                   | 41 |

| Table 17. ATA-100 44-pin Connector Pin-out (J2K3)                                                  | 42 |

| Table 18. SATA Connector Pin-Out (J1K3, J1J7, J1J4, J1H3, J1H1, J1G6)                              | 43 |

| Table 19. External RJ-45 Serial B Port Pin-Out (J9A2)                                              | 43 |

| Table 20. Internal 9-pin Serial A Header Pin-Out (J1B1)                                            | 44 |

| Table 21. Stacked PS/2 Keyboard and Mouse Port Pin-Out (J9A1)                                      | 44 |

| Table 22. External USB Connector Pin-Out (JA6A1, JA6A2)                                            | 45 |

| Table 23. Internal USB Connector Pin-Out (J1J8)                                                    | 45 |

| Table 24. SSI Fan Connector Pin-out (J9K1,J5K1,J1K4, J1K5, J2K2, J2K5, J9B1, J9B2)                 | 46 |

| Table 25. Recovery Jumpers (J1J1, J1J2)                                                            | 47 |

| Table 26: Board Design Specifications                                                              | 52 |

| Table 27. Dual-Core Intel <sup>®</sup> Xeon <sup>®</sup> processor 5000 sequence DP TDP Guidelines | 53 |

| Table 28. Load Ratings                                                                             | 54 |

| Table 29. Transient Load Requirements                                                              | 56 |

| Table 30. Capacitive Loading Conditions                                                            | 56 |

| Table 31. Ripple and Noise                                                                         | 57 |

| Table 32. Output Voltage Timing                                                                    | 57 |

#### Intel® Server Board S5000VSA TPS

#### **List of Tables**

| Table 33. Turn On / Off Timing             | 58 |

|--------------------------------------------|----|

| Table 34. BMC Sensors                      | 68 |

| Table 35: POST Progress Code LED Example   | 77 |

| Table 36: Diagnostic LED POST Code Decoder | 78 |

< This page intentionally left blank. >

### 1. Introduction

This Technical Product Specification (TPS) provides board specific information detailing features, functionality, and high level architecture of the Intel® Server Board S5000VSA. The *Intel® S5000 Server Board Family Datasheet* should also be referenced for more in depth detail of various board sub-systems including Chipset, BIOS, and system management.

In addition, design level information for specific sub-systems can be obtained by ordering the External Product Specifications (EPS) or External Design Specifications (EDS) for a given sub-system. EPS and EDS documents are not publicly available and must be ordered through your local Intel representative.

## 1.1 Chapter Outline

This document is divided into the following chapters

- Chapter 1 Introduction

- Chapter 2 Intel<sup>®</sup> Server Board S5000VSA Overview

- Chapter 3 Functional Architecture

- Chapter 4 Platform Management

- Chapter 5 Connector/Header Location and Pin-out

- Chapter 6 Configuration Jumpers

- Chapter 7 Light Guided Diagnostics

- Chapter 8 Design and Environmental Specifications

- Chapter 9 Regulatory and Certification Information

- Appendix A Integration and Usage Tips

- Appendix B Sensor Tables

- Appendix C POST Code Diagnostic LEDs

## 1.2 Server Board Use Disclaimer

Intel Corporation server boards contain a number of high-density VLSI and power delivery components that need adequate airflow to cool. Intel ensures through its own chassis development and testing that when Intel server building blocks are used together, the fully integrated system will meet the intended thermal requirements of these components. It is the responsibility of the system integrator who chooses not to use Intel developed server building blocks to consult vendor datasheets and operating parameters to determine the amount of air flow required for their specific application and environmental conditions. Intel Corporation cannot be held responsible if components fail or the server board does not operate correctly when used outside any of their published operating or non-operating limits.

## 2. Intel<sup>®</sup> Server Board S5000VSA Overview

The Intel® Server Board S5000VSA is a monolithic printed circuit board with features that were designed to support the pedestal server markets.

## 2.1 Intel<sup>®</sup> Server Board S5000VSA Feature Set

| Feature           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Processors        | 771-pin LGA sockets supporting 1 or 2 Dual-Core Intel <sup>®</sup> Xeon <sup>®</sup> processors 5000 sequence, with system bus speeds of 1066 MHz or 1333 MHz                                                                                                                                                                                                                                                                                                                                                                                              |

| Memory            | Maximum support for 16GB. Four or eight (based on board SKU type) DIMM slots supporting fully buffered DIMM technology (FBDIMM) memory. 240-pin DDR2-533 and DDR2-667 FBDIMMs may be used. Note: Full DIMM heat spreaders are required.                                                                                                                                                                                                                                                                                                                    |

| Chipset           | Intel® S5000V chipset, including: Intel® S5000V MCH Intel® ESB2-E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| I/O Control       | <ul> <li>External connections:</li> <li>Stacked PS/2* ports for keyboard and mouse</li> <li>DB9 Serial port</li> <li>Two RJ45 NIC connectors for 10/100/1000 Mb connections</li> <li>Seven USB 2.0 ports (4 rear, 2 front, 1 floppy)</li> <li>Internal Connections:</li> <li>1 RS-232 Serial</li> <li>1 P-ATA133</li> <li>Six SATA (300MB) connectors with integrated RAID 0/1/5/10 support</li> <li>SSI-compliant front panel header</li> <li>SSI-compliant 24-pin main power connector, supporting the ATX-12V standard on the first 20 pins.</li> </ul> |

| Video             | On-board ATI* ES1000 video controller with 16MB DDR SDRAM external video memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Hard Drives       | Support for six SATA-300 hard drives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| LAN               | Intel® 82563EB dual port controller for 10/100/1000 Mbit/sec Ethernet LAN connectivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Fans              | Support for two processor fans, five system fans, and one memory fan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| System Management | Support for Intel® System Management Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

## 2.2 Server Board Layout

### 2.2.1 Server Board Connector and Component Layout

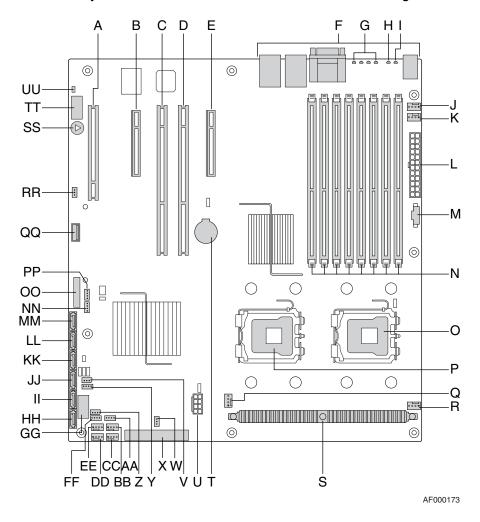

The following figure shows the board layout of the server board. Each connector and major component is identified by a number or letter and is identified below the figure.

| A. PCI 32/33 Slot 1            | B. PCI Express* x4 Slot 3  | C. PCI-X* 64/133 Slot 4      |

|--------------------------------|----------------------------|------------------------------|

| D. PCI-X* 64/100 Slot 5        | E. PCI Express* x4 Slot 6  | F. Back Panel I/O Ports      |

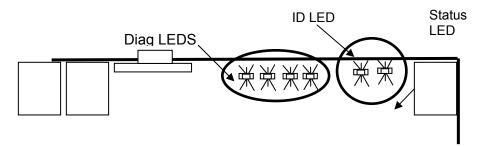

| G. Diagnostic LEDs             | H. System ID LED           | I. System Status LED         |

| J. System Fan 6                | K. System Fan 5            | L. Main Power Connector      |

| M. Auxiliary Signal Connector  | N. DIMM Sockets            | O. Processor 1 Socket        |

| P. Processor 2 Socket          | Q. Processor Fan 2 Header  | R. Processor Fan 1 Header    |

| S. Processor Voltage Regulator | T. Battery                 | U. Processor Power Connector |

| V. IPMB Header                 | W. SAS RAID5 Key           | X. IDE Connector             |

| Y. LCP Header                  | Z. SAS_SES2                | AA. SAS SGPIO                |

| BB. System Fan 3               | CC. System Fan 4           | DD. System Fan 2             |

| EE. System Fan 1               | FF. SATA SGPIO             | GG. USB 4-5                  |

| HH. SATA 0 Connector           | II. SATA 1 Connector       | JJ. SATA 2/SAS 0 Connector   |

| KK. SATA 3/SAS 1 Connector     | LL. SATA 4/SAS 2 Connector | MM. SATA 5/SAS 3 Connector   |

| NN. Backplane Connector B      | OO. Front Panel Header     | PP. Backplane Connector A    |

| QQ. USB 6                      | RR. SATA RAID5 Key         | SS. Speaker                  |

| TT. Serial B EMP Connector     | UU. Chassis Intrusion      |                              |

Figure 1. Major Board Components

### 2.2.2 Server Board Mechanical Drawings

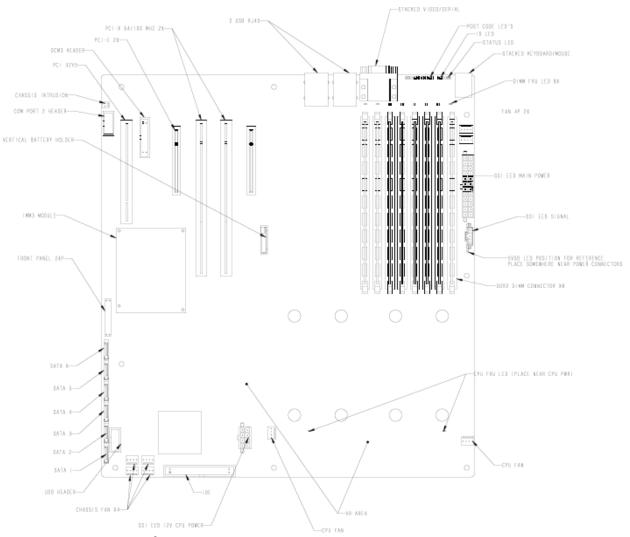

Figure 2. Intel<sup>®</sup> Server Board S5000VSA – Key Connectors and LED Indicators

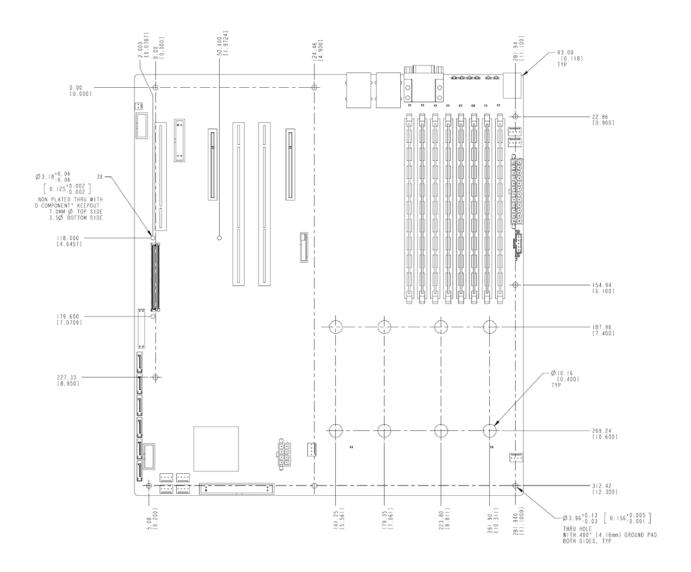

Figure 3. Intel<sup>®</sup> Server Board S5000VSA – Mounting Hole Locations

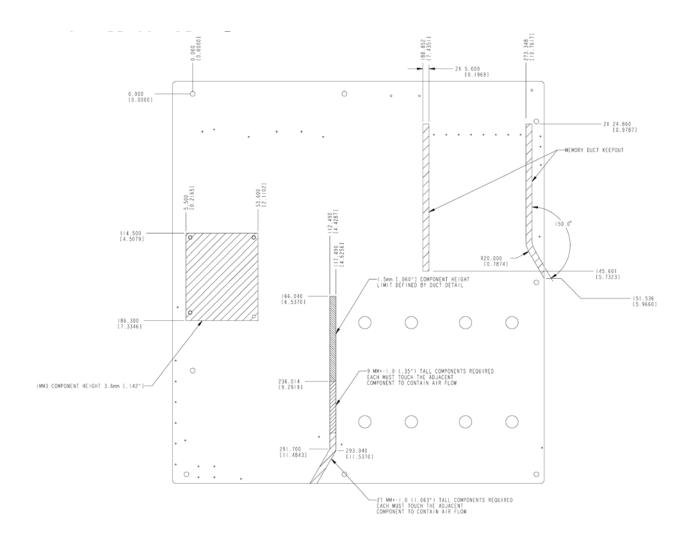

Figure 4. Intel<sup>®</sup> Server Board S5000VSA – Duct keepout Detail

### 2.2.3 Server Board ATX I/O Layout

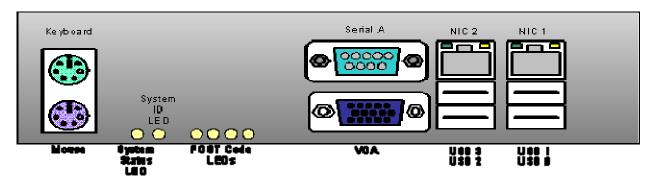

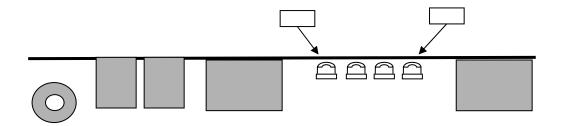

The drawing below shows the layout of the rear I/O components for the server board.

Figure 5. Intel<sup>®</sup> Server Board S5000VSA ATX I/O Layout

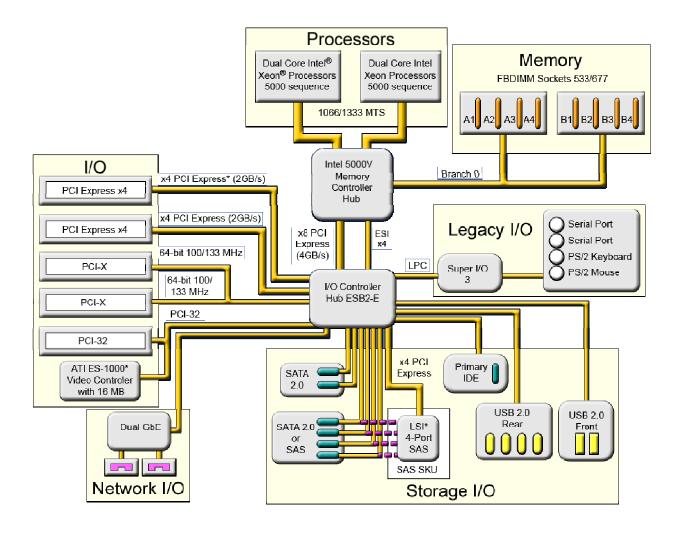

### 3. Functional Architecture

The architecture and design of the Intel® Server Board S5000VSA is based on the Intel® S5000V Chipset. The chipset is designed for systems based on the Intel processor code named "Dempsey/Woodcrest" and supports FSB frequencies of 1066 MTS/1333 MTS. The chipset contains two main components: the Memory Controller Hub (MCH) for the host bridge, and the I/O controller hub for the I/O subsystem. The Intel® S5000V chipset uses the Enterprise South Bridge (ESB2-E) for the I/O controller hub. This chapter provides a high-level description of the functionality associated with each chipset component and the architectural blocks that make up the Intel® Server Board S5000VSA. For more detailed descriptions for each of the functional architecture blocks, see the *Intel® S5000 Server Board Family Datasheet*.

Figure 6. Intel® Server Board S5000VSA Functional Block Diagram

## 3.1 S5000V Controller Hub (MCH)

The S5000V Memory Controller Hub (MCH) chip is packaged in a 1432 pin FCBGA package. It supports the Dual-Core Intel<sup>®</sup> Xeon<sup>®</sup> processor 5000 sequence (1067 MTS/1333 MTS) package. This package uses the matching LGA771 socket.

#### 3.1.1 Processor Sub-system

The MCH supports a FSB frequency of 267MHz/333MHz (1067 MTS/1333 MTS) using a point to point dual inline bus (DIB) processor system bus interface. Each processor FSB supports peak address generation rates of 133 million addresses per second. Both FSB data buses are quad pumped 64-bits which allow peak bandwidths of 8.5GB/s (1067MT/s) or 10.7GB/s (1333MT/s) depending on the processor used.

The support circuitry for the processor sub-system consists of the following:

- Dual LGA771 zero insertion force (ZIF) processor sockets

- Processor host bus AGTL+ support circuitry

- Reset configuration logic

- Processor module presence detection logic

- BSEL detection capabilities

- CPU signal level translation

- Common Enabling Kit Direct Chassis Attach (CEK DCA) CPU retention support

For detailed information about the functional architecture provided by the chipset, see the *Intel® S5000 Server Board Family Datasheet*.

#### 3.1.1.1 Processor Support

The server board supports one or two Dual-Core Intel<sup>®</sup> Xeon<sup>®</sup> processors 5000 sequence utilizing a 667MHz/1067MHz/1333MHz front side bus with frequencies starting at 2.67 GHz. Previous generations of the Intel<sup>®</sup> Xeon<sup>®</sup> processor are not supported on the server board. See the following table for a list of supported processors.

| Processor Family                               | System Bus<br>Speed | Core Frequency | Cache   | Watts | Support |

|------------------------------------------------|---------------------|----------------|---------|-------|---------|

| Intel® Xeon® processor                         | 533 MHz             | All            |         |       | No      |

| Intel <sup>®</sup> Xeon <sup>®</sup> processor | 800 MHz             | All            |         |       | No      |

| Dual-Core Intel® Xeon® processor 5030          | 667 MHz             | 2.67 GHz       | 2x 2 MB | 95    | Yes     |

| Dual-Core Intel® Xeon® processor 5050          | 667 MHz             | 3.0 GHz        | 2x 2 MB | 95    | Yes     |

| Dual-Core Intel® Xeon® processor 5060          | 1066 MHz            | 3.2 GHz        | 2x 2 MB | 130   | Yes     |

| Dual-Core Intel® Xeon® processor 5063          | 1066 MHz            | 3.2 GHz        | 2x 2 MB | 95    | Yes     |

| Dual-Core Intel® Xeon® processor 5080          | 1066 MHz            | 3.73 GHz       | 2x 2 MB | 130   | Yes     |

| Dual-Core Intel® Xeon® processor 51xx          | 1333/1066           | TBD            | TBD     | TBD   | Yes     |

|                                                | MHz                 |                |         |       |         |

**Table 1. Processor Support Matrix**

#### 3.1.1.2 Processor Population Rules

When two processors are installed, both must be of identical revision, core voltage, and bus/core speed. When only one processor is installed, it must be in the socket labeled CPU1. The other socket must be empty.

Processors must be populated in sequential order. Processor socket 1 (CPU1) must be populated before processor socket 2 (CPU2).

The board is designed to provide up to 130A of current per processor. Processors with higher current requirements are not supported.

No terminator is required in the second processor socket when using a single processor configuration.

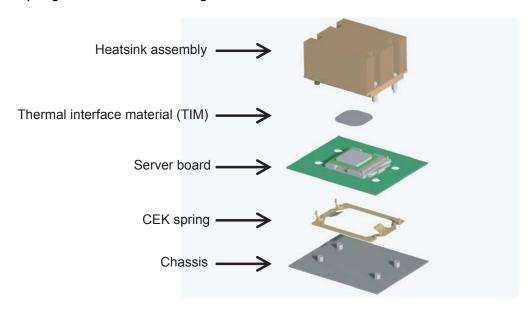

#### 3.1.1.3 Common Enabling Kit (CEK) Design Support

The server board complies with Intel's Common Enabling Kit (CEK) processor mounting and heat sink retention solution. The server board ships with a CEK spring snapped onto the underside of the server board, beneath each processor socket. The heat sink attaches to the CEK, over the top of the processor and the thermal interface material (TIM). See the figure below for the stacking order of the chassis, CEK spring, server board, TIM, and heat sink.

The CEK spring is removable, allowing for the use of non-Intel heat sink retention solutions.

**Figure 7. CEK Processor Mounting**

#### 3.1.2 Memory Sub-system

The MCH masters two fully buffered DIMM (FBDIMM) memory channels. FBDIMM memory utilizes a narrow high speed frame oriented interface referred to as a channel. On the server board, the two channels are routed to eight DIMM slots and are capable of supporting registered DDR2-533 and DDR2-667 FBDIMM memory (stacked or unstacked). Peak FBDIMM memory data bandwidth in dual channel mode is 6.4GB/s (2x3.2GB/s) with DDR2-533/PC2-4200 (3.75ns@CL4) and 8.0GB/s (2x4.0GB/s) with DDR2-667/PC2-5300 (3.0ns@CL5).

To boot the system, the system BIOS on the server board uses a dedicated I<sup>2</sup>C bus to retrieve DIMM information needed to program the MCH memory registers. The following table provides the I<sup>2</sup>C addresses for each DIMM slot.

Table 2. I<sup>2</sup>C Addresses for Memory Module SMB

| Address |

|---------|

| 0xA0    |

| 0xA2    |

| 0xA4    |

| 0xA6    |

| 0xA0    |

| 0xA2    |

| 0xA4    |

| 0xA6    |

|         |

#### 3.1.2.1 Supported Memory

The server board supports up to eight (four for the 4-DIMM SKU) DDR2-533 or DDR2-667 Fully Buffered DIMM memory (FBDIMM memory). DDR2 DIMMS that are not Fully Buffered are NOT supported on this server board. The following tables show the maximum memory configurations supported using specified memory technology.

Table 3. Maximum 8 DIMM System Memory Configruation – x8 (width) Single Rank = 1 load

| DRAM Technology x8 Single Rank (64M8=64M x 8b=16M x 8b x 4 banks) | Maximum Capacity |

|-------------------------------------------------------------------|------------------|

| 512 Mb (Density)                                                  | 2 GB             |

|                                                                   |                  |

Table 4. Maximum 8 DIMM System Memory Configuration – x4 (width) Dual Rank = 2 loads

| DRAM Technology x4 Dual Rank(128M4=128M x4b=32M x 4b x 4 banks) | Maximum Capacity |

|-----------------------------------------------------------------|------------------|

| 512 Mb (Density)                                                | 4 GB             |

|                                                                 |                  |

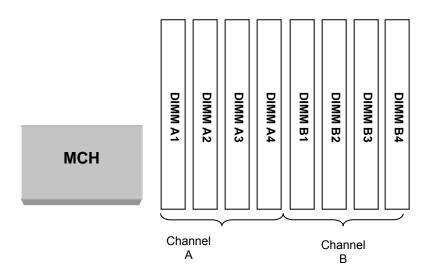

#### 3.1.2.2 DIMM Population Rules

DIMM population rules depend on the operating mode of the memory controller. On the server board DIMMs must be populated in the following order: A1 and B1, A2 and B2, etc. The server board will support population of DIMMs with different speed ratings, however this is not recommended. The overall system memory speed will be determined by the slowest DIMM populated.

#### 3.1.2.2.1 Minimum Configuration

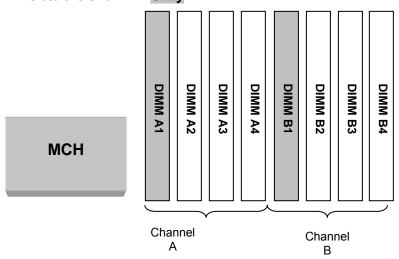

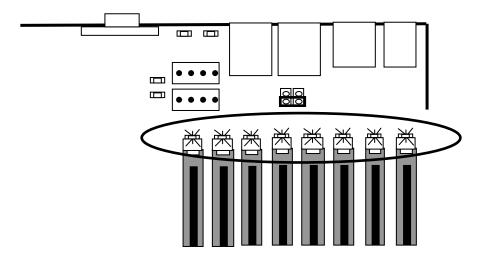

The following diagram shows a minimum two DIMM memory configuration for the server board. Populated DIMM slots are shown in **Gray**.

#### Figure 8. Minimum Two DIMM Memory Configuration

Note: The server board BIOS supports single DIMM mode operation although this is generally not recommended for "performance" applications. This configuration is <u>only</u> supported with a 512MB FBDIMM installed in DIMM slot A1.

#### 3.1.2.2.2 Memory upgrades

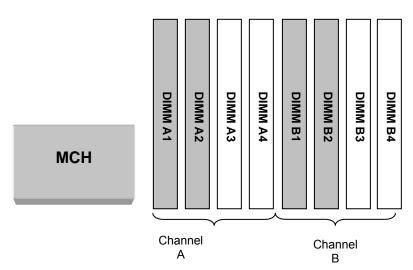

The minimum memory upgrade increment is two DIMMs. The DIMMs must cover the same slot number on both channels. DIMMs that cover a slot number must be identical with respect to size, speed, and organization. DIMMs that cover adjacent slot positions need not be identical.

When adding two DIMMs to the configuration shown in Figure 10, the DIMMs should be populated in DIMM slots A2 and B2 as shown in the following diagram. Populated DIMM slots are shown in **Gray**.

Figure 9. Recommended Four DIMM Configuration

## 3.2 Enterprise South Bridge (ESB2-E)

The ESB2-E is a multi-function device that is a merging of four distinct functions: an ICH6 like controller; a PCI-X\* Bridge, a Gigabit Ethernet controller and a BMC. Each function within the ESB2-E has its own set of configuration registers. Once configured, each appears to the system as a distinct hardware controller.

A primary role of the ESB2-E is to provide the gateway to all PC-compatible I/O devices and features. The baseboard uses the following ESB2-E features:

- PCI-X\* bus interface

- Six Channel SATA interface w/SATA Busy LED Control

- Dual Gbe MAC

- Baseboard Management Controller (BMC)

- Single ATA interface, with Ultra DMA 100 capability

- Universal Serial Bus 2.0 (USB) interface

- LPC bus interface

- PC-compatible timer/counter and DMA controllers

- APIC and 8259 interrupt controller

- Power management

- System RTC

- General purpose I/O

This section describes the function of each I/O interface and how they operate on the server board

#### 3.2.1 PCI Sub-system

#### 3.2.1.1 PCI Express\* Overview

The MCH supports three x4 PCI Express\* ports. PCI Express is a high speed, frame based, serial I/O interface that can achieve peak theoretical bandwidths of 2 GB/s per x4 port (1 GB/s in each direction). These ports can be configured in a number of different combinations thus enhancing the scalability and performance of the system. Below is the PCI Express port configuration used by the server board.

#### **Server Board Configuration:**

**Port 0 (x4):** Otherwise known as the Enterprise Server Interface (ESI) port, Port [0] connects to the ESB2-E. Although the ESI port follows the standard PCI Express\* protocol, it also executes proprietary commands only used between Intel chipsets.

**Port 2 and Port 3 (2 x4 = x8):** Otherwise known as the Direct Memory Access (DMA) port, x4 Ports [3:2] combine to create a x8 port which also connects to the ESB2-E. The DMA port follows the standard PCI Express\* protocol, but allows direct access to memory for higher speed I/O transactions.

#### 3.2.1.2 PCI Express\* Hot-Plug

The server board does not support PCI Express\* hot-plug.

#### 3.2.2 SATA Support

The integrated Serial ATA (SATA) controller of the ESB2-E provides six SATA ports on the server board. The SATA ports can be enabled/disabled and/or configured by accessing the BIOS Setup Utility during POST.

The SATA function in the ESB2-E has dual modes of operation to support different operating system conditions. In the case of native IDE-enabled operating systems, the ESB2-E has separate PCI functions for serial and parallel ATA. To support legacy operating systems, there is only one PCI function for both the serial and parallel ATA ports. The MAP register provides the ability to share PCI functions. When sharing is enabled, all decode of I/O is done through the SATA registers. A software write to the Function Disable Register (D31, F0, offset F2h, bit 1) causes Device 31, Function 1 (IDE controller) to hidden, and its configuration registers are not

used. The SATA Capability Pointer Register (offset 34h) will change to indicate that MSI is not supported in combined mode.

The ESB2-E SATA controller features two sets of interface signals that can be independently enabled or disabled. Each interface is supported by an independent DMA controller. The ESB2-E SATA controller interacts with an attached mass storage device through a register interface that is equivalent to that presented by a traditional IDE host adapter. The host software follows existing standards and conventions when accessing the register interface and follows standard command protocol conventions.

SATA interface transfer rates are independent of UDMA mode settings. SATA interface transfer rates will operate at the bus' maximum speed, regardless of the UDMA mode reported by the SATA device or the system BIOS.

#### 3.2.2.1 SATA RAID

The Intel® Embedded RAID Technology II solution, available with the ESB2-E ICH6, offers data striping for higher performance (RAID Level 0), alleviating disk bottlenecks by taking advantage of the dual independent SATA controllers integrated in the ESB2-E ICH6. There is no loss of PCI resources (reguest/grant pair) or add-in card slot.

Intel® Embedded RAID Technology II functionality requires the following items:

- ESB2-E ICH6

- Intel<sup>®</sup> Embedded RAID Technology II Option ROM must be on the server board

- Intel<sup>®</sup> Application Accelerator RAID Edition drivers, most recent revision

- Two SATA hard disk drives

Intel® Embedded RAID Technology II is not available in the following configurations:

- The SATA controller in compatible mode

- Intel<sup>®</sup> Embedded RAID Technology II has been disabled

#### 3.2.2.2 Intel® Embedded RAID Technology II Option ROM

The Intel® Embedded RAID Technology II for SATA Option ROM provides a pre-OS user interface for the Intel® Embedded RAID Technology II implementation and provides the ability for an Intel® Embedded RAID Technology II volume to be used as a boot disk as well as to detect any faults in the Intel® Embedded RAID Technology II volume(s) attached to the Intel® RAID controller.

#### 3.2.3 Parallel ATA (PATA) Support

The integrated IDE controller of the ESB2-E ICH6 provides one IDE channel. This IDE channel is capable of supporting one optical drive. A standard high density 40-pin IDE connector interfaces with the primary IDE channel signals. The IDE channels can be configured and enabled or disabled by accessing the BIOS Setup Utility during POST.

The BIOS supports the ATA/ATAPI Specification, version 6 or later. It initializes the embedded IDE controller in the chipset south-bridge and the IDE devices that are connected to these devices. The BIOS scans the IDE devices and programs the controller and the devices with their optimum timings. The IDE disk read/write services that are provided by the BIOS use PIO mode, but the BIOS will program the necessary Ultra DMA registers in the IDE controller so that the operating system can use the Ultra DMA modes.

The BIOS initializes and supports ATAPI devices such as LS-120/240, CDROM, CD-RW and DVD.

The BIOS initializes and supports SATA devices just like PATA devices. It initializes the embedded the IDE controllers in the chipset and any SATA devices that are connected to these controllers. From a software standpoint, SATA controllers present the same register interface as the PATA controllers. Hot plugging SATA drives during the boot process is not supported by the BIOS and may result in undefined behavior

#### 3.2.3.1 Ultra ATA/133

The IDE interface of the ESB2-E ICH DMA protocol redefines signals on the IDE cable to allow both host and target throttling of data and transfer rates of up to 133MB/s.

#### 3.2.3.2 IDE Initialization

The BIOS supports the ATA/ATAPI Specification, version 6 or later. The BIOS initializes the embedded IDE controller in the chipset (ESB2-E ICH) and the IDE device that is connected to these devices. The BIOS scans the IDE device and programs the controller and the device with their optimum timings. The IDE disk read/write services that are provided by the BIOS use PIO mode, but the BIOS programs the necessary Ultra DMA registers in the IDE controller so that the operating system can use the Ultra DMA Modes.

#### 3.2.4 USB 2.0 Support

The USB controller functionality integrated into ESB2-E ICH6 provides the server board with the interface for up to seven USB 2.0 ports. Four external connectors are located on the back edge of the server board. One internal 1x10 header is provided, capable of supporting an additional two optional USB 2.0 ports. There is also a USB port intended for USB floppy support.

## 3.3 Video Support

The server board provides an ATI\* ES1000 PCI graphics accelerator, along with 16MB of video DDR SDRAM and support circuitry for an embedded SVGA video sub-system. The ATI\* ES1000 chip contains an SVGA video controller, clock generator, 2D and 3D engine, and RAMDAC in a 272-pin PBGA. One 4Mx16x4bank DDR SDRAM chip provides 16MB of video memory.

The SVGA sub-system supports a variety of modes, up to  $1600 \times 1200$  resolution in 8 / 16 / 32bpp modes under 2D, and up to  $1024 \times 768$  resolution in 8 / 16 / 24 / 32bpp modes under 3D. It also supports both CRT and LCD monitors up to 100 Hz vertical refresh rate.

Video is accessed using a standard 15-pin VGA connector found on the back edge of the server board.

On-board video can be disabled using the BIOS Setup Utility or when an add-in video card is installed. The system BIOS also provides the option for dual video operation when an add-in video card is configured in the system.

#### 3.3.1.1 Video Modes

The chip supports all standard IBM\* VGA modes. The following table shows the 2D/3D modes supported for both CRT and LCD.

| 2D Mode   | Refresh Rate (Hz)   | 2D Video Mode Support |           |           |           |

|-----------|---------------------|-----------------------|-----------|-----------|-----------|

|           |                     | 8 bpp                 | 16 bpp    | 24 bpp    | 32 bpp    |

| 640x480   | 60, 72, 75, 90, 100 | Supported             | Supported | Supported | Supported |

| 800x600   | 60, 70, 75, 90, 100 | Supported             | Supported | Supported | Supported |

| 1024x768  | 60, 72, 75, 90, 100 | Supported             | Supported | Supported | Supported |

| 1280x1024 | 43, 60              | Supported             | Supported | Supported | Supported |

| 1280x1024 | 70, 72              | Supported             | _         | Supported | Supported |

| 1600x1200 | 60, 66              | Supported             | Supported | Supported | Supported |

| 1600x1200 | 76, 85              | Supported             | Supported | Supported | -         |

Table 5. Video Modes

#### 3.3.1.2 Video Memory Interface

The memory controller sub-system of the ES1000 arbitrates requests from direct memory interface, the VGA graphics controller, the drawing coprocessor, the display controller, the video scalar, and hardware cursor. Requests are serviced in a manner that ensures display integrity and maximum CPU/coprocessor drawing performance.

The server board supports a 16MB (4Meg x 16-bit x 4 banks) DDR SDRAM device for video memory. The following table shows the video memory interface signals:

| Signal Name | I/O Type | Description             |

|-------------|----------|-------------------------|

| V_M_CAS_N   | 0        | Column Address Select   |

| V_M_CKE     | 0        | Clock Enable for Memory |

| V_M_CS_N    | 0        | Chip Select for Memory  |

| V_M_DQM[10] | 0        | Memory Data Byte Mask   |

| V_M_QS[10]  | I/O      | Memory Data Strobe      |

| V_M_CLK     | I        | Memory Clock            |

| V_M_CLK_N   | I        | Memory Clock Compliment |

| V_M_MA[150] | 0        | Memory Address Bus      |

| V_M_MD[150] | I/O      | Memory Data Bus         |

| V_M_RAS_N   | 0        | Row Address Select      |

| V_M_WE_N    | 0        | Write Enable            |

**Table 6. Video Memory Interface**

#### 3.3.1.3 **Dual Video**

The BIOS supports single and dual video modes. The dual video mode is enabled by default.

- In single mode (Dual Monitor Video=Disabled), the onboard video controller is disabled when an add-in video card is detected.

- In dual mode (Onboard Video=Enabled, Dual Monitor Video=Enabled), the onboard video controller is enabled and will be the primary video device. The external video card will be allocated resources and is considered the secondary video device. BIOS Setup provides user options to configure the feature as follows:

Video is routed to the rear video connector by default. When a monitor is plugged in to the front panel video connector, the video is routed to it and the rear connector is disabled. This can be done by hot plugging the video connector.

| Onboard Video      | Enabled  |                                              |

|--------------------|----------|----------------------------------------------|

|                    | Disabled |                                              |

| Dual Monitor Video | Enabled  | Shaded if onboard video is set to "Disabled" |

|                    | Disabled |                                              |

## 3.4 Network Interface Controller (NIC)

The Intel® 82563EB Gigabit Platform LAN Connect is a dual, compact Physical Layer Transceiver (PHY) component designed for 10/100/1000 Mbps operation.

The Intel® 82563EB device is based upon proven PHY technology integrated into Intel Gigabit Ethernet Controllers. The physical layer circuitry provides a standard IEEE 802.3 Ethernet interface for 1000BASE-T, 100BASE-TX, and 10BASE-T applications (802.3, 802.3u, and 802.3ab). The 82563EB device is capable of transmitting and receiving data at rates of 1000 Mbps, 100 Mbps, or 10 Mbps

Each Network Interface Controller (NIC) drives two LEDs located on each network interface connector. The link/activity LED (to the left of the connector) indicates network connection when on, and Transmit/Receive activity when blinking. The speed LED (to the right of the connector) indicates 1000-Mbps operation when amber, 100-Mbps operation when green, and 10-Mbps when off. The table below provides an overview of the LEDs.

| LED Color          | LED State | NIC State                   |

|--------------------|-----------|-----------------------------|

|                    | Off       | 10 Mbps                     |

| Green/Amber (Left) | Green     | 100 Mbps                    |

|                    | Amber     | 1000 Mbps                   |

| Green (Right)      | On        | Active Connection           |

|                    | Blinking  | Transmit / Receive activity |

Table 7. NIC Status LED

## 3.5 Super I/O

Legacy I/O support is provided by using a National Semiconductor\* PC87427 Super I/O device. This chip contains all of the necessary circuitry to control two serial ports, one parallel port, floppy disk, and PS/2-compatible keyboard and mouse. Of these, the server board supports the following:

- GPIOs

- Two serial ports

- Removable media drives

- Floppy controller

- Keyboard and mouse support

- Wake up control

- System health support

#### 3.5.1.1 Serial Ports

The server board provides two serial ports: an external DBb-9 serial port, and an internal DH10 serial header.

Serial B is an optional port, accessed through a 9-pin internal DH-10 header. A standard DH10 to DB9 cable can be used to direct serial B to the rear of a chassis. The serial B interface follows the standard RS232 pin-out as defined in the following table.

Serial A Header Pin-out Pin Signal Name DCD 1 2 DSR 2 RX 3 3 4 RTS 4 5 TX 5 6 6 CTS 7 8 DTR 7 8 RI 9 **GND**

Table 8. Serial A Header Pin-out

The rear DB-9 serial A port is a fully functional serial port that can support any standard serial device.

#### 3.5.1.2 Removable Media Drives

The BIOS supports removable media devices, including 1.44MB floppy removable media devices and optical devices such as a CD-ROM drive or a read-only DVD-ROM drive. The BIOS supports booting from USB mass storage devices connected to the chassis USB port, such as a USB key device.

The BIOS supports USB 2.0 media storage devices that are backward compatible to the USB 1.1 specification.

#### 3.5.1.3 Floppy Disk Controller

The server board does not support a floppy disk controller (FDC) interface. However, the system BIOS does recognize USB floppy devices.

#### 3.5.1.4 Keyboard and Mouse Support

Dual stacked PS/2 ports, located on the back edge of the server board, are provided for keyboard and mouse support. Either port can support a mouse or keyboard. Neither port supports hot plugging.

#### 3.5.1.5 Wake-up Control

The super I/O contains functionality that allows various events to control the power-on and power-off the system.

## 4. Platform Management

The platform management sub-system on the server board is based on the integrated Baseboard Management Controller (BMC) features of the ESB2-E. In addition, the on board platform management subsystem consists of communication buses, sensors, system BIOS, and system management firmware.

For additional information, see the Intel® \$5000 Server Board Family Datasheet.

Platform management involves:

- 1. ACPI implementation specific details

- 2. System monitoring, control and response to thermal, voltage and intrusion events

- 3. BIOS security

#### 4.1 Power Button

The system power button is connected to the ESB2-E component. When the button is pressed the ESB2-E receives the signal and transitions the system to the proper sleep-state as determined by the OS and software. If the power button is pressed and held for 4 seconds the system will power off (S5 state). This feature is called "power button override" and particularly helpful in the case of system hang and locking up the system. The server board is fully *ACPI 1.0a* compliant.

## 4.2 Sleep States Supported

The ESB2-E controls the system sleep states. States S0, S1, S4 and S5 are supported. Either the BIOS or an OS invokes the sleep states. This is done in response to a power button being pressed or an inactivity timer countdown. Normally the OS determines which sleep state to transition into. However a 4 second power button over-ride event places the system immediately into S5. When transitioning into a software-invoked sleep state, the ESB2-E will attempt to gracefully put the system to sleep by first going into the CPU C2 state.

#### 4.2.1 S0 State

This is the normal operating state, even though there are some power savings modes in this state using CPU Halt and Stop Clock (CPU C1and C2 states). S0 affords the fastest wake up response time of any sleep state because the system remains fully powered and memory is intact.

#### 4.2.2 S1 State

This state is entered via a CPU sleep signal from the ESB2-E (CPU C3 state). The system remains fully powered and memory contents intact but the CPUs enter their lowest power state. The OS uses ACPI drivers to disable bus masters for uni-processor configurations, while the OS flushes and invalidates caches before entering this state in multiprocessor configurations. Wake-up latency is slightly longer in this state than S0, however power savings are quite improved from S0.

#### 4.2.3 S4 State

This state is called Suspend to Disk. From a hardware perspective it is equivalent to an S5 (Soft Off) state, however, S4 has the distinction of avoiding a full boot sequence. The OS is responsible for saving the system context in a special partition on the hard drive. Although the system must power up and fully boot, boot time to an application is reduced because the computer is returned to the same system state as when the preceding power-off occurred.

#### 4.2.4 S5 State

This state is the normal off state whether entered through the power button or soft off. All power is shut off except for the logic required to restart. In this state, several "wake up events" are supported. The system only remains in the S5 state while the power supply is plugged into the wall. If the power supply is unplugged from the wall, this is considered a mechanical OFF or G3.

## 4.3 Wakeup Events

The types of wake events and wake up latencies are related to the actual power rails available to the system in a particular sleep state as well as to the location in which the system context is stored. Regardless of the sleep state, wake on the power button is always supported except in a 'mechanical off' situation. When in a sleep state, the server board complies with the *PCI 2.2 Specification* by supplying the optional 3.3V standby voltage to each PCI slot as well as the PME signal. This enables any compliant PCI card to wake the system up from any sleep state except mechanical off.

#### 4.3.1 Wakeup from S1 Sleep State

During S1, the system is fully powered permitting support for wake on USB, wake on PS/2 Keyboard/Mouse, wake on RTC alarm, and wake on PCI PME. Wake on USB, wake on PS/2 Keyboard/Mouse and wake on RTC alarm are not supported by the server board POE BIOS.

#### 4.3.2 Wakeup from S3 Sleep State (BFAD Workstation Only)

In S3 state, wake from USB, PS/2, power button, and LAN are supported.

#### 4.3.3 Wakeup from S4 and S5 States

In S4 or S5, wake from power button and LAN are supported.

## 4.4 AC Power Failure Recovery

The design supports two modes of operation with regard to AC power recovery. The user can select (via a BIOS Setup Screen) whether the system should power back up or remain off after AC is restored. The ESB2-E does not rely on BIOS to boot and check system status in the case of AC failure. The ESB2-E contains a register variable named "afterG3" which BIOS can set based on user configuration input. The ESB2-E internally examines after it detects an AC recovery.

## 4.5 PCI PM Support

The *PCI Power Management Specification* calls out three areas to be compliant: the system reset signal must be held low when in a sleep state, the system must support the

PCI PME signal and the system should provide 3.3v standby to the PCI slots. The server board design complies with the PCI PM Specification and the *PCI 2.2 Specification* for optional 3.3V standby voltage to be supplied to each PCI, PCI-X\*, and PCI Express\* slots. This support allows any compliant PCI, PCI-X, or PCI Express adapter card to wake the system up from any sleep state except mechanical off. Because of the limited amount of power available on 3.3V standby, the user and the OS must configure the system carefully following the *PCI Power Management Specification*.

#### 4.5.1 RESET# Control

The ESB2-E always drives the Platform Reset signal (LOW or HIGH), even when the system is in a sleep state. This is required for PCI power management. Any device that may be active will be able to sample this signal to know that the system is in a reset condition.

#### 4.5.2 PCI Vaux

All standard PCI, PCI-X\*, and PCI Express\* slots are provided with 3.3 V aux power to support wake events from all sleep states. The MIC2169 power supply will deliver 4 A of 5 VSB, which in turn is regulated to 3.3 VSB when the system is in the S4 or S5 sleep state. Standby 3.3V power will not be connected to x1 PCI Express debug slots and these debug slots will not wake events.

## 4.6 System Management

The LM94 monitors the majority of the system voltages. The LM94 also monitors the VID signals from the Dual-Core Intel<sup>®</sup> Xeon<sup>®</sup> processor 5000 sequence. All voltage levels can be read from the LM94 via the SMBus.

#### 4.6.1 CPU Thermal Management

Each CPU will monitor its own core temperature and thermally manage itself when it reaches a certain temperature. The system will also utilize the internal CPU diode(s) to monitor the die temperature. The diode pins are routed to the diode input pins in the LM94. For valid thermal diode configurations for dual core processors, refer to thermal diode options table. The LM94 can be programmed to force the CPU fans to full speed operation when it senses the CPU core temperature exceeding a specific value. In addition, the LM94 itself has an on chip thermal monitor. The placement of the LM94 will allow it to monitor the incoming ambient temperature that is blown in by the chassis input fan in front of the processors.

## 4.7 System Fan Operation

The server board utilizes both the LM94 and super I/O to monitor and control the fans in the system. Both devices use pulse width modulated (PWM) outputs that can modulate the voltage across the fans, providing a variable duty-cycle to affect a reduced DC voltage from nominal 12 VDC. The fan drive circuit and headers are the new 4-pin type. The 4-pin fans now have a dedicated PWM input for speed control, in addition to the standard ground, +12V, and tachometer pins. Both the LM94 and super I/O have fan tachometer inputs that can be used to monitor and control fan speeds. All fan tachometer data can be extracted from the controllers via the SMBus. The fan speed control circuit does not control the power supply fan. To support limited controller and/or firmware functionality during power on and debug activities, each PWM output has a bypass jumper that will cause all fans to run at full speed and ignore the PWM control.

Each CPU fan has its own dedicated PWM input and tachometer output, so they can be controlled and monitored independently. The LM94 will be dedicated to processor fan speed control and monitor, and the SIO will drive and monitor the remaining fans in the system: the chassis and memory fans.

Refer to fan manual override jumpers table for identification of fan speed override jumpers. Refer to the National Semiconductor\* PC87427 and LM94 (National Semiconductor LM93) specifications regarding fan monitor and control capabilities and programming requirements.

# 4.8 Light Guided Diagnostics - System Status and FRU LEDs

The standard system status LEDs for PWR/SLP, HDD and other LEDs as specified in SSI EEB are supported on the front panel header.

For 10/100/1000 LAN, status LEDs are supported through the back panel 10/100/1000 RJ45 Jack and the front panel per the SSI-EEB specification. The dual color LED indicates the LAN speed at 10Mbit/s (off), 100Mbit/s (green) or 1000 Mbit/s (yellow). The green link LED represents both link integrity (on/off) as well as LAN activity (blinking).

Table 9 Summary of LEDs on the Intel® Server Board S5000VSA

| Name                | Color | Condition | What it describes                                     |

|---------------------|-------|-----------|-------------------------------------------------------|

| Power/Sleep         | Green | ON        | Power On                                              |

| (S1/S3)             | Green | BLINK     | Sleep (S1/S3)                                         |

|                     | -     | OFF       | Power Off (also S4)                                   |

| Status              | Green | ON        | System READY                                          |

| Front-Panel &       | Green | BLINK     | System Degraded (memory, CPU failure)                 |

| Baseboard           | Amber | ON        | BW/BIOS: Fatal Alarm. Post error/NMI event            |

|                     |       |           | FW Only: CPU/Terminator Missing, Fan,                 |

|                     |       |           | Temparature, Voltage, visible if fatal error causes a |

|                     |       |           | power down                                            |

|                     | Amber | BLINK     | FAN Alarm. Temparature or Voltage Non-Critical        |

|                     |       |           | Alarm, Drive Fault                                    |

|                     | -     | OFF       |                                                       |

| FANS                | -     | OFF       | DIAG(FIV)                                             |

|                     | Amber | ON        | BIOS/FW: In redundant fan system, if one or more      |

|                     |       |           | fans are missing during POST, BIOS should turn on     |

|                     |       |           | LED                                                   |

|                     |       |           | FW: FAN Failure Alarm                                 |

| CPU                 | -     | OFF       |                                                       |

|                     | Amber | ON        | Fatal Alarm.CPU/Terminator Missing/CPU Failure        |

| DIMM                | -     | OFF       |                                                       |

|                     | Amber | ON        | Memory failure - fatal                                |

| Progress Code       |       |           | See Flash tab for details of the code                 |

| HP PCI              | ?     | ?         | ?                                                     |

| Telco FP            | ?     | ?         | ?                                                     |

| GEM424              | Green |           | Hard Disk Drive Access                                |

| (SATA/SAS)          |       |           | NOTE: Only some SATA drive support this feature       |

| GEM359 (SCSI)       |       | BLINK     |                                                       |

| , ,                 | Amber | ON        | Disk drive fault                                      |

| Vitesse             | Green |           | HDD in Standby/Stopped. HDD may be removed.           |

| (SATA/SAS)          |       | OFF       | LED normally OFF                                      |

| NOTE: Amber ON,     | Green |           | Spin-up/Spin-down                                     |

| and GREEN OFF       |       | BLINK 1s  | LED on 0.5s, OFF 0.5s, 50% duty cycle of 1s           |

| indicates its OK to | Green | ON        | Active/Idle power                                     |

| remove HDD          | Green |           | Formatting                                            |

|                     |       |           | LED ON for 1s, OFF for 1s, 50% duty-cycle of 2s       |

|                     |       | BLINK 2s  |                                                       |

|                     | Amber | ON        | Fault                                                 |

|                     | Amber |           | Flashing - On 1s, OFF 1s, 50% duty-cycle of 2s        |

|                     |       | BLINK     | Indicates Rebuild                                     |

| Power Supply        |       |           |                                                       |

| HDD ACTIVITY        | Green | BLINK     | Hard Disk Drive Access                                |

|                     | -     | OFF       | No Access                                             |

| LAN#1-Link/Act      | Green | ON        | Link                                                  |

|                     | Green | BLINK     | LAN Access (off when there is traffic)                |

|                     | -     | OFF       | Disconnect                                            |

| LAN#1-Speed         | Green | ON        | Green, link speed is 100Mbits/sec                     |

|                     | Amber | ON        | Amber, link speed is 1000Mbits/sec                    |

|                     | -     | OFF       | OFF, link speed is 10Mbits/sec                        |

| LAN#2-Link/Act      | Green | ON        | Link                                                  |

|                     | Green | BLINK     | LAN Access (off when there is traffic)                |

|                     | -     | OFF       | Disconnect                                            |

| LAN#2-Speed         | Green | ON        | Green, link speed is 100Mbits/sec                     |

|                     | Amber | ON        | Amber, link speed is 1000Mbits/sec                    |

|                     | -     | OFF       | OFF, link speed is 10Mbits/sec                        |

| Identification      | Blue  | ON        | Unit selected for identification                      |

|                     | Blue  | BLINK     | blink under software control                          |

|                     | _     | OFF       | No Identification                                     |

# 5. Connector / Header Locations and Pin-outs

## 5.1 Board Connector Information

The following section provides detailed information regarding all connectors, headers and jumpers on the server board. Table 10 lists all connector types available on the board and corresponding reference designators printed on silkscreen.

**Table 10. Board Connector Matrix**

| Connector                | Quantity | Reference Designators                          | Connector Type     | Pin   |

|--------------------------|----------|------------------------------------------------|--------------------|-------|

|                          |          |                                                |                    | Count |

| Power supply             | 3        | J4K1                                           | CPU Power          | 8     |

|                          |          | J9C1                                           | Main Power         | 24    |

|                          |          | J9D1                                           | P/S Aux            | 5     |

| CPU                      | 2        | J1000, J2000                                   | CPU Sockets        | 771   |

| Main Memory              | 8        | U7B1, U7B2, U7B3, U8B1, U8B2, U8B3, U9B1, U9B2 | DIMM Sockets       | 240   |

| RAID Key                 | 1        | J1D1                                           | Key Holder         | 3     |

| IDE                      | 1        | J2K3                                           | Shrouded<br>Header | 44    |

| System Fans              | 4        | J1K4, J1K5, J2K2, J2K5                         | Header             | 4     |

| Memory Fans              | 2        | J9B1, J9B2                                     | Header             | 4     |

| CPU Fans                 | 2        | J5K1, J9K1                                     | Header             | 4     |

| Battery                  | 1        | BT4E1                                          | Battery Holder     | 3     |

| Keyboard/Mouse           | 1        | J9A1                                           | PS2, stacked       | 12    |

| Rear 2xUSB/LAN connector | 2        | JA6A1, JA6A2                                   | External           | 16    |

| Serial Port B            | 1        | J1B1                                           | Header             | 9     |

| Serial Port A            | 1        | J7A1                                           | External, RJ45     | 10    |

| Video Connector          | 1        |                                                | External, D-Sub    | 15    |

| Front panel, main        | 1        | J1F1                                           | Header             | 24    |

| Front panel, USB         | 1        | J1J8                                           | Header             | 10    |

| Intrusion detect         | 1        | J1A1                                           | Header             | 2     |

| Serial ATA               | 2        | J1K3, J1J7                                     | Header             | 7     |

| SATA/SAS                 | 4        | J1J4, J1H3, J1H1, J1G6                         | Header             | 7     |

| IPMB/LCP                 | 1        | J1J5                                           | Header             | 4     |

| IPMB                     | 1        | J1J6                                           | Header             | 3     |

| Configuration<br>Jumpers | 3        | J1J1, J1J2, J1J3                               | Jumper             | 3     |

## **5.2 Power Connectors**

The main power supply connection is obtained using an SSI compliant 2x12 pin connector (J9C1). In addition, there are two additional power related connectors; one SSI compliant 2x4 pin power connector (J4K1) providing support for additional 12V, and one SSI compliant 1x5 pin connector (J9D1) providing I<sup>2</sup>C monitoring of the power supply. The following tables define their pin-outs.

Pin Signal Color Pin Signal Color 1 +3.3Vdc 13 +3.3Vdc Orange Orange 2 +3.3Vdc 14 -12Vdc Blue Orange 3 **GND** Black 15 **GND** Black 4 +5Vdc Red 16 PS ON Green 5 **GND** Black 17 GND Black **GND** 6 +5Vdc Red 18 Black 7 **GND** Black 19 **GND** Black NC 8 PWR GND 20 White Gray 9 5VSB Purple 21 +5Vdc Red 10 +5Vdc +12Vdc Yellow 22 Red 11 +12Vdc Yellow 23 +5Vdc Red 12 +3.3Vdc 24 **GND** Orange Black

**Table 11. Power Connector Pin-out (J9C1)**

**Table 12. 12V Power Connector Pin-out (J4K1)**

| Pin | Signal | Color        |

|-----|--------|--------------|

| 1   | GND    | Black        |

| 2   | GND    | Black        |

| 3   | GND    | Black        |

| 4   | GND    | Black        |

| 5   | +12Vdc | Yellow/Black |

| 6   | +12Vdc | Yellow/Black |

| 7   | +12Vdc | Yellow/Black |

| 8   | +12Vdc | Yellow/Black |

Color Pin Signal SMB\_CLK\_ESB\_FP\_PWR\_R Orange 1 SMB DAT ESB FP PWR R 2 Black 3 SMB ALRT 3 ESB R Red 4 3.3V SENSE-Yellow 5 3.3V SENSE+ Green

Table 13. Power Supply Signal Connector Pin-out (J1K1)

### **5.3 Control Panel Connector**

The server board provides an optional 24-pin SSI control panel connector (J1F1) for use with reference chassis. The following tables provide the pin-out for this connector.

Signal Name Front Panel Pin-out Pin Signal Name Pin P5V\_STBY P5V Front Panel Pinout 3 Key O O 4 P5V STBY Power O FP PWR LED L FP COOL FLT LED R 5 6 Cool Fault LED O O P5V P5V STBY 8 HDD System O O 9 HDD\_LED\_ACT\_R 10 FP STATUS LED2 R LED Fault O O FP PWR BTN L LAN ACT A L 11 12 Power O O LAN A **Button** 13 GND Link / Act 14 LAN LINKA L O O 15 Reset Button Reset PS I2C 5VSB SDA 16 O O **SMBus** Button GND O O PS I2C 5VSB SCL 17 18 Sleep Intruder O O 19 FP\_SLP\_BTN\_L 20 FP CHASSIS INTRU **Button** LAN B O O 21 GND 22 LAN ACT B L Link / Act NMI O O 23 FP NMI BTN L 24 LAN LINKB L 25 Key 26 Key O O ID LED 27 P5V\_STBY 28 P5V\_STBY O O 29 FP ID LED L O O 30 FP STATUS LED1 R ID Button O O FP\_ID\_BTN\_L P5V 31 32 33 GND 34 FP HDD FLT LED R

Table 14. Front Panel SSI Standard 24-pin Connector Pin-out (J1F1)

## 5.4 I/O Connectors

## 5.4.1 VGA Connector

The following table details the pin-out definition of the VGA connector (J7A1).

**Table 15. VGA Connector Pin-Out (J7A1)**

| Pin | Signal Name     | Description                   |

|-----|-----------------|-------------------------------|

| 1   | V_IO_R_CONN     | Red (analog color signal R)   |

| 2   | V_IO_G_CONN     | Green (analog color signal G) |

| 3   | V_IO_B_CONN     | Blue (analog color signal B)  |

| 4   | TP_VID_CONN_B4  | No connection                 |

| 5   | GND             | Ground                        |

| 6   | GND             | Ground                        |

| 7   | GND             | Ground                        |

| 8   | GND             | Ground                        |

| 9   | TP_VID_CONN_B9  | No Connection                 |

| 10  | GND             | Ground                        |

| 11  | TP_VID_CONN_B11 | No connection                 |

| 12  | V_IO_DDCDAT     | DDCDAT                        |

| 13  | V_IO_HSYNC_CONN | HSYNC (horizontal sync)       |

| 14  | V_IO_VSYNC_CONN | VSYNC (vertical sync)         |

| 15  | V_IO_DDCCLK     | DDCCLK                        |

#### 5.4.2 NIC Connectors

The server board provides two RJ45 NIC connectors oriented side by side on the back edge of the board (JA6A1, JA6A2). The pin-out for each connector is identical and is defined in the following table.

Table 16. RJ-45 10/100/1000 NIC Connector Pin-Out (JA6A1, JA6A2)

| Pin     | Signal Name           |

|---------|-----------------------|

| 1       | GND                   |

| 2       | P1V8_NIC              |

| 3       | NIC_A_MDI3P           |

| 4       | NIC_A_MDI3N           |

| 5       | NIC_A_MDI2P           |

| 6       | NIC_A_MDI2N           |

| 7       | NIC_A_MDI1P           |

| 8       | NIC_A_MDI1N           |

| 9       | NIC_A_MDI0P           |

| 10      | NIC_A_MDI0N           |

| 11 (D1) | NIC_LINKA_1000_N (LED |

| 12 (D2) | NIC_LINKA_100_N (LED) |

| 13 (D3) | NIC_ACT_LED_N         |

| 14      | NIC_LINK_LED_N        |

| 15      | GND                   |